Matching transistors layouts is important to minimize variations in electrical characteristics. This is especially true for analog and mixed-signal circuits, such as differential amplifiers, where symmetrical behaviour is critical for high precision and low distortion. Similar to current mirrors, matching transistors ensure accurate current replication, which is critical for biasing and amplification stages. In this article, I will explain several of the important design rules that help in the reduction of mismatch.

1. Same temperature conditions

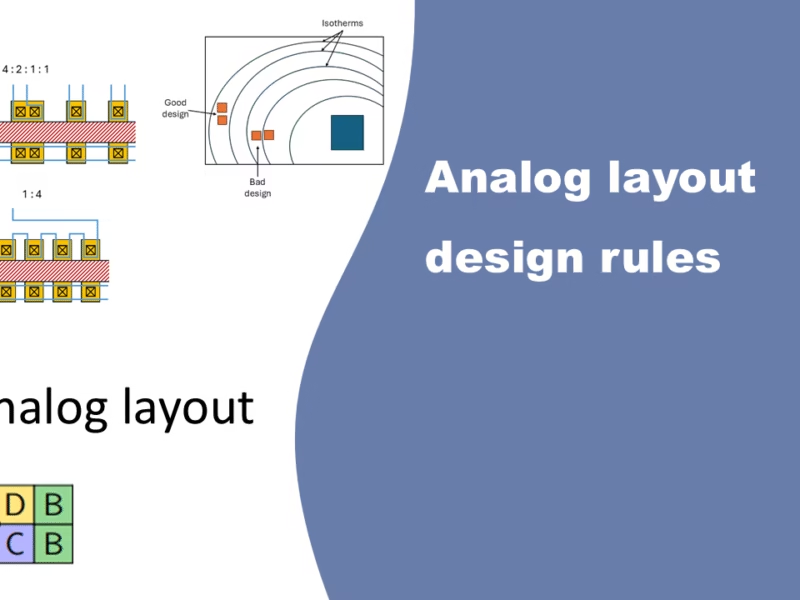

Let’s start with an obvious (but difficult) layout condition. For optimal matching between two transistors for example, both devices must operate along the same isotherm. Large chips often experience high temperatures, and while silicon is a good thermal conductor, temperature gradients can still arise. For instance, power devices on one side of a chip can create localized heating, affecting other areas.

When power devices heat the chip on the right side, they generate isotherms extending to other regions. Input transistors of an op-amp or differential circuit should ideally be positioned along these isotherms. If not, internal thermal resistance can act like a feedback resistor, limiting the open-loop gain (refer to the source for more details).

The trick with this rule is, is that it can be challenging to find these isotherms.

2. Current orientation matching

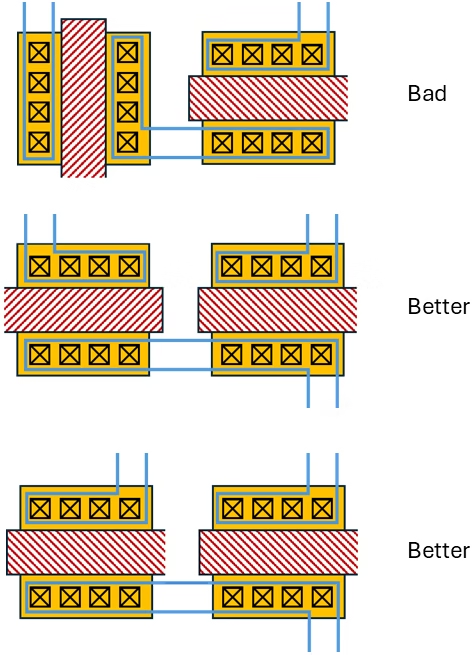

Crystal orientation plays a critical role in achieving good matching in transistors. A crystal’s structure, including properties like density varies depending on direction. Consequently, the mobility μ parameter is not identical in all directions. This phenomenon is highlighted in the following examples:

- In the first case, current in one transistor flows perpendicular to the current in the other one. This misalignment leads to poor matching.

- In contrast, the second and third examples show better configurations. While slight variations in source contact resistance may occur due to connection placement, these differences are generally minimal and less impactful.

3. Area over perimeter ratio

A highly effective way to improve layout design for better matching is to maintain a consistent area-to-perimeter ratio or use identical shapes for all transistors, ensuring they are the same size. This is because rounding effects on edges and corners have a more pronounced impact on smaller transistors compared to larger ones.

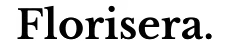

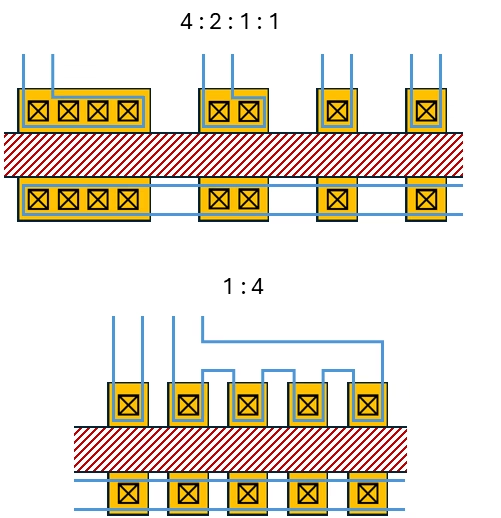

For example, consider the figure below, where the transistor sizes follow relative ratios of 4:2:1:1. These ratios may lack precision because edge rounding disproportionately affects the smaller transistors (size 1) compared to the larger ones (size 4).

A more precise approach involves using identical shapes for all transistors and connecting them in parallel. This method ensures a uniform area-to-perimeter ratio, minimizing the relative impact of local errors. For instance, implementing a 1:4 ratio using this technique yields significantly higher accuracy. While this layout style, common in bipolar transistor designs, requires more space, it greatly improves matching performance. It is generally true that making it bigger improves the matching performance overall.

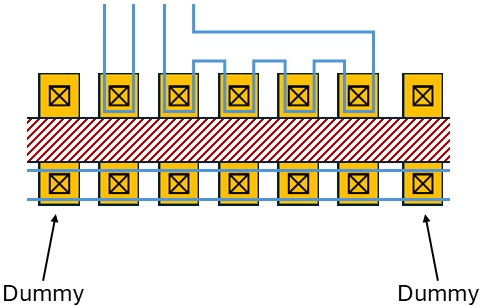

4. End dummies

In places with multiple equal structures (such as transistors, capacitors, resistors, etc.), the ones on the outside never match that well. The reason for that is, that these outside structures see different neighbours. Imagine a 10×10 grid of transistors; all the ones on the inside see transistors all around them, while the outer rim only sees it on the inside and nothing on the outside. Effects of processing, such as etching, contact holes, etc. will be different. That is the reason why dummy structures are placed on the end.

These dummies are not used, and in the case of transistors transistors their VGS = 0. In the figure below you see the example of the previous section with the use of end dummies to improve the performance of all the active transistors. tl;dr, the are only present to make sure that the processes are done homogeneously for all active transistors.

5. Centroid layout

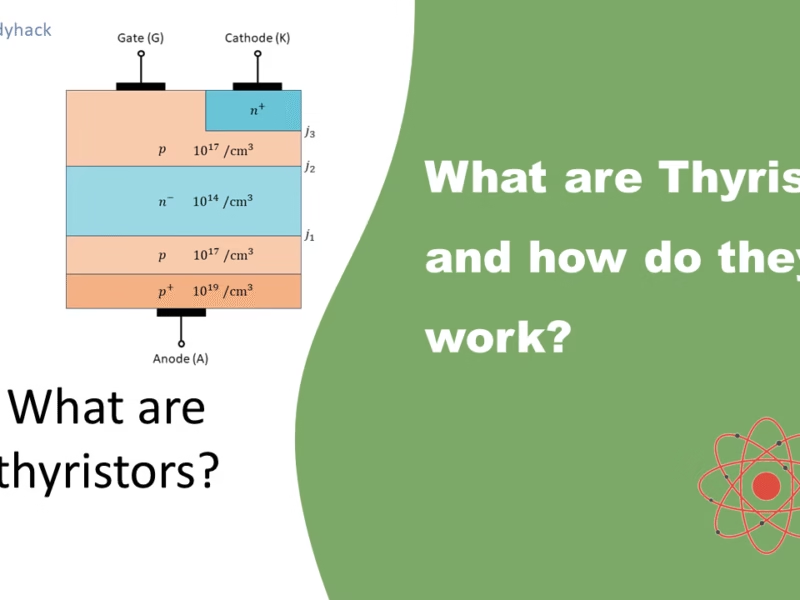

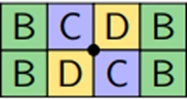

One important layout style to reduce mismatch is the common centroid (CC) layout. In this layout, all segments are placed so that their centroids coincide. For example, the layout in Figure 5 shows a CC layout where the segments C & D have a common centroid marked with the black dot. The segments B on the outer rim could be considered dummies, and can even be extended further to include a top and bottom row. This layout is used in my previous article on how to design an OTA.

The idea behind using CC layouts, is that they cancel out linear systematic variations due to first order process gradients (in oxide thickness, …). Under these assumptions, the CC criterion ensures that the sum of variations over all segments cancel each other out. To get the best out of a CC layout, you want your array to occupy as little space as possible and have a summetry around both x- and y-axis so that the devices are balanced and mirrored both horizontally (x-axis) and vertically (y-axis).